Zarlink Semiconductor has developed an improved version of its sub-micron BiCMOS process technology that it is targeting for higher power and higher temperature power management chips. Dubbed the WP process, it is available now for low cost prototyping using a multi-project wafer processing service. The process combines Zarlink Analog Foundry's 20V 5GHz WPX/Y analog bipolar technology with a set of CMOS control aspects that are crucial in the fabrication of electronic components responsible for controlling power and extending battery life.

"Most competing BiCMOS offerings are CMOS-centric with poor bipolar components. Building on our WP bipolar power management process expertise, we have integrated our 0.8µ CMOS process to develop the only true analog bipolar BiCMOS technology available. Our next steps are to incorporate our DMOS technology onto this process to permit the development of a BCDMOS process capability," said Dr. Peter Osborne, Chief Technology Officer, Zarlink Analog Foundry. Osborne said the improved transistor has up to twice the beta VA product and more consistent voltage output over a range of input currents. "This power management performance enhancement is in direct response to requirements from customers who are using our process technologies in increasingly demanding applications."

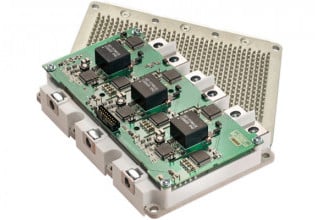

The company says it developed the WP series 15-layer process specifically for industrial power management applications, including dc-dc power bricks, mobile telephone battery power management and all linear power management applications. The bipolar process features high-value poly resistors and nitride capacitors and two-layer metal that allows low current circuits to be built with high packing densities. The technologies are suitable for greater than 20 and 22V power management applications.