With power converters demanding higher power density, transistors must be accommodated in an ever decreasing board space. Beyond GaN-based power transistors' ability to improve electrical efficiency, they must also be more thermally efficient. A paper titled, "Thermal Evaluation of Chip-Scale Packaged Gallium Nitride Transistors" by David Reusch, Johan Strydom, and Alex Lidow with Efficient Power Conversion Corporation and presented at this week's IEEE Applied Power Electronics Conference, evaluated the thermal performance of chip-scale packaged enhancement-mode GaN field effect transistors (eGaN® FETs) and compared their in-circuit electrical and thermal performance with state-of-art silicon MOSFETs. The paper concluded with the proposal of a thermal figure of merit (FOM) for designers to use as a tool to quickly compare the thermal efficiency of device packaging technologies.

The authors open the paper with the observation, “There are five basic requirements for a better transistor; (1) lower on-resistance, (2) faster switching speeds, (3) better thermal conductivity, (4) smaller size, and (5) lower cost. From time to time different technologies, such as GaAs or SiC, have improved on one or more of these basic requirements. Gallium nitride, grown on a silicon crystal, can improve upon all of the characteristics just listed when compared with the best silicon devices available, and in this paper we will focus on their improved thermal performance in chip-scale packages.â€

The thermal efficiency of a package can be determined by comparing two parameters, RÆŸJC and RÆŸJB, normalized to the package area. RÆŸJC is the thermal resistance from junction-to-case; this is the thermal resistance from the active part of the eGaN FET to the top of the silicon substrate, including the sidewalls. RÆŸJB is the thermal resistance from junction-to-board; this is the thermal resistance from the active part of the eGaN FET to the printed circuit board (PCB).

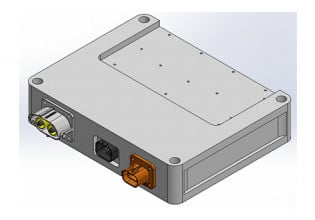

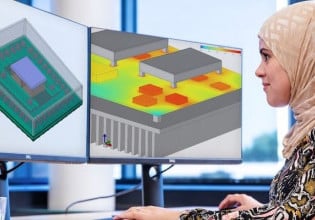

To quantify the in-circuit thermal performance of various packages, a series of thermal evaluation boards were developed. And to create a more complete in-circuit thermal model of the eGaN FET based designs, the thermal evaluation boards were tested at a variety of operating points with various levels of airflow, under two test conditions, with and without a heat sink.

The thermal evaluation boards, meant to accurately represent in-circuit operating conditions, were tested as buck converters with an input voltage of 48V, an output voltage of 12V, and a switching frequency of 300 kHz. The paper continued with a comparison of chip-scale-packaged eGaN-FET-based and Si MOSFET-based power converters including both electrical and thermal performance comparisons.

The authors stated that, "Due to the lack of an industry standard on test conditions for thermal steady state, it is difficult to compare such data from different sources. As a result, it is common industry practice for efficiency and power loss measurements to use 'instantaneous' efficiency measurements. These are not truly instantaneous since the measurements take several seconds, much longer than time constants for typical semiconductor die. However, they reduce many of the heating effects and form a good baseline measurement."

In their conclusion, the authors observe that: "Figures of merit have been used for almost half of a century to compare device technologies. FOMs, generally tailored for specific applications, are a simple tool to quickly compare different technologies ability to improve transistor performance. While the majority of FOMs give valuable insight into the electrical performance achievable with a given device technology, little insight is given into thermal performance at the application level, which is also critical in power converter design. In this section, we will introduce a thermal figure of merit for designers to use as a tool to quickly compare the thermal efficiency of given devices packaging technology. This thermal FOM will be compared for the eGaN FET and Si MOSFET packaging technologies used in this paper."

The paper also states: the thermal capability of a package can be determined by two parameters, RÆŸJB and RÆŸJC, the junction-to-board and junction-to-case thermal impedances. These thermal impedances scale with the size of a given package technology, with a larger device having lower thermal impedance. The thermal efficiency of a package is related to its ability to dissipate heat based on a given chip area.

The thermal efficiency of a package can be determined by comparing two parameters, RÆŸJC and RÆŸJB, normalized to the package area. RÆŸJC is the thermal resistance from junction-to-case; this is the thermal resistance from the active part of the eGaN FET to the top of the silicon substrate, including the sidewalls. RÆŸJB is the thermal resistance from junction-to-board; this is the thermal resistance from the active part of the eGaN FET to the printed circuit board (PCB). For this path the heat must transfer through the solder bars/balls to the copper traces on the board. To compare the thermal efficiency of a given packaging technology a thermal figure of merit is proposed:

Where ADEVICE is the size of the packaged device. For design cases where heat can be removed through both the PCB and backside of the device (RθBA ≈ RθCA):

For cases where the dominant heat removal path is through the printed circuit board (PCB) (RÆŸBA << RÆŸCA): RÆŸEQ = RÆŸJB.

And for cases where the dominant heat removal path is the backside of the device (RÆŸBA >> RÆŸCA): RÆŸEQ = RÆŸJC.

Assuming the device can be effectively cooled through the PCB and the backside of the device, the thermal FOM can be given by:

"Comparing the thermal FOM, where a lower FOM represents improved package thermal efficiency, for eGaN FETs chip-scale packages and the Si MOSFET packages used for comparison in this paper, the thermal efficiency advantages of the chip-scale package can be seen - with the eGaN FET packaging having almost a 2x reduction in FOMTH compared to the best Si MOSFET package. The chip-scale package offers efficient double-sided cooling and the best thermal performance based on the size of the chip," the authors continued.

In this paper, the authors evaluated the thermal performance of chip-scale packaged GaN transistors. They concluded, "For high voltage lateral GaN transistors, all of the electrical connections are located on the same side of the die, allowing for the elimination of complex, performance limiting two sided packaging common in vertical Si power MOSFETs. Chip-scale packaging is a more efficient form of packaging that reduces the resistance, inductance, size, thermal impedance, and cost of power transistors, enabling unmatched in-circuit performance."